Why stacking chips like pancakes could mean a huge leap for laptops. Imagine laptops that are incredibly powerful, yet incredibly thin and light. This revolutionary concept, utilizing the stacking of multiple chips, promises a significant performance boost. Current laptop designs are limited by the size and power consumption of individual chips. The “pancake” approach, where chips are layered vertically, offers a promising solution to these limitations, potentially leading to faster processors, improved battery life, and more compact devices.

This article delves into the exciting world of chip stacking, exploring the technical challenges, potential benefits, and future implications for laptop design. We’ll examine the current state of chip technology, the advantages and disadvantages of this stacking method, and the innovative thermal management strategies needed to make this concept a reality. From manufacturing processes to the potential impact on laptop form factors, this comprehensive guide will leave you wondering about the future of computing.

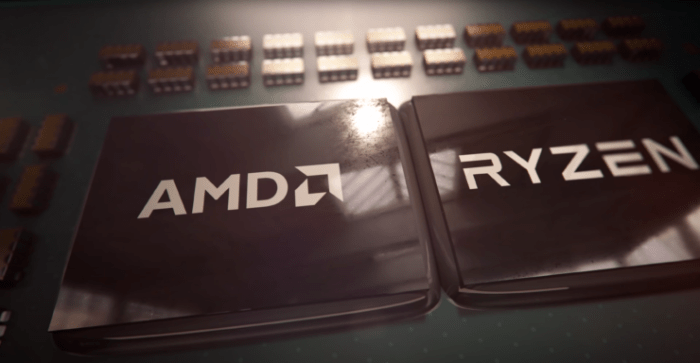

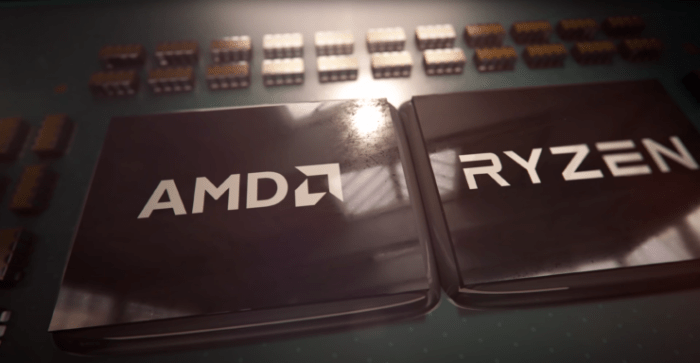

Introduction to Chip Stacking

Laptop processors, the brains of our portable computing devices, are constantly evolving. Current designs, while powerful, are reaching physical limitations. The increasing demand for faster, more efficient, and smaller laptops necessitates innovative approaches to processor architecture. One such approach is chip stacking, a technique promising significant performance gains.The current state of laptop chip design involves a complex interplay of various components.

Modern processors utilize multiple dies, each performing specific functions. Connecting these dies, and managing their communication and power distribution, is a critical part of the design process. Heat dissipation and minimizing power consumption remain significant challenges. The limitations of traditional methods are now motivating the exploration of more radical approaches.

Current Laptop Processor Design

Contemporary laptop processors often use a multi-chip module (MCM) approach. This involves combining multiple chips, each with specialized functions, onto a single substrate. Examples include Intel’s Foveros and AMD’s chiplets. These techniques allow for increased functionality and potential performance, but are limited by the physical constraints of current interconnect technology. Interconnects between the various chips introduce delays and limitations on overall system performance.

Limitations of Traditional Designs

Traditional laptop processor designs face several limitations:

- Thermal constraints: The increasing number of transistors and higher operating frequencies generate significant heat, requiring sophisticated cooling solutions that can add bulk and complexity to the laptop design.

- Interconnect limitations: Connecting different processor components, especially with complex communication patterns, can lead to bottlenecks in data transfer and overall performance.

- Die size and packaging: Integrating more transistors and functions onto a single die often leads to increased die size and complexity in the packaging process, resulting in higher costs and limitations on overall system miniaturization.

Alternative Approaches to Increase Processing Power

Several avenues exist for enhancing laptop processing power beyond traditional approaches:

- 3D chip stacking: This innovative technique vertically stacks multiple chips, eliminating the need for extensive interconnects and significantly reducing signal delays. This allows for higher integration densities and performance.

- Improved interconnect technologies: The development of advanced interconnects, like those used in high-speed networking, is critical to facilitating efficient data transfer between stacked chips.

- Advanced packaging techniques: Innovations in packaging methods are crucial for effectively managing the thermal and electrical demands of tightly integrated stacked chips. These advancements include better thermal interface materials and improved cooling solutions.

Comparison of Traditional vs. Stacked Chips

| Feature | Traditional Chips | Stacked Chips |

|---|---|---|

| Interconnect | 2D, planar interconnects | 3D, stacked interconnects |

| Performance | Limited by 2D interconnect constraints | Potentially higher performance due to reduced interconnect delays |

| Power Consumption | Can be higher due to longer signal paths | Potentially lower due to shorter signal paths and better thermal management |

| Integration Density | Limited by die size | Higher integration density |

| Cost | Potentially lower for individual components | Potentially higher due to complexity of stacking process |

The “Pancake” Approach

The concept of stacking chips like pancakes, a method often referred to as 3D chip stacking, offers a compelling path towards significantly enhancing laptop performance and shrinking their size. This approach leverages vertical space instead of relying solely on horizontal expansion, a crucial factor in the ongoing miniaturization trend in electronics. This innovative technique has the potential to dramatically improve processing power, graphics capabilities, and overall system efficiency within a compact form factor.The “pancake” approach involves layering multiple integrated circuits (ICs) vertically, much like stacking pancakes.

This contrasts with traditional approaches where components are arranged in a two-dimensional plane. By integrating chips vertically, manufacturers can create a denser and more powerful computing system while potentially reducing the overall size of the device. This method allows for more complex and sophisticated circuits to be placed in a smaller area, opening the door to unprecedented performance improvements.

Imagine stacking computer chips like pancakes – it could revolutionize laptops, making them smaller and more powerful. This kind of innovation, pushing the boundaries of miniaturization, is similar to how Flume 2 helps conserve water and prevent home flooding burst pipes by efficiently managing water flow. The potential for compacting powerful components is huge, paving the way for laptops that are unbelievably thin and light, yet packed with processing power.

Potential Benefits of 3D Chip Stacking

This method holds significant advantages over conventional chip integration techniques. Firstly, it significantly increases the density of components. By stacking chips vertically, the amount of processing power and memory that can be packed into a given space is dramatically increased. Secondly, the reduced distances between components leads to faster data transfer rates. This results in improved performance for tasks that rely heavily on communication between different parts of the system, such as complex calculations or high-resolution graphics rendering.

Finally, the reduced overall size of the system can translate to thinner and lighter laptops, enhancing portability and usability.

Stacking chips like pancakes could revolutionize laptops, offering significantly improved performance and power efficiency. It’s mind-blowing how much faster our tech could become! Speaking of amazing deals, did you know my favorite baby bassinet is 210 during Cyber Monday sales? my favorite baby bassinet is 210 during cyber monday sales This kind of efficiency in both tech and baby products is a huge win! Ultimately, this stacking chip technology could lead to thinner, faster, and more powerful laptops, making them a true game-changer.

Comparison with Other Chip Integration Methods

Compared to traditional planar chip integration, 3D chip stacking offers a substantial advantage in terms of density and performance. While techniques like chip-on-board (CoB) and package-on-package (PoP) are commonly used, they typically have limitations in terms of achieving the same level of integration and performance density. These conventional approaches do not allow for the same vertical stacking and interconnection capabilities as 3D stacking, which is a key differentiator.

Challenges in Implementing Pancake Chip Stacking

While the benefits are considerable, several challenges must be addressed for successful implementation. One significant hurdle is the development of advanced materials and manufacturing processes capable of handling the precise and intricate stacking of chips. The need for extremely precise alignment and bonding between layers is crucial for reliable functionality. Moreover, ensuring thermal management within the densely packed system is vital to prevent overheating.

The complexity of the design and the need for advanced testing procedures also pose challenges in the development process.

Advantages and Disadvantages of 3D Stacking

| Advantages | Disadvantages |

|---|---|

| Increased component density | Complex manufacturing process |

| Faster data transfer rates | High precision requirements |

| Reduced system size | Thermal management challenges |

| Improved performance | Potential for increased cost |

| Enhanced portability | Higher design complexity |

Thermal Management

Stacking multiple chips like pancakes in laptops presents a significant thermal challenge. The close proximity of these components dramatically increases heat generation, potentially leading to overheating and performance degradation. Effective thermal management is crucial for maintaining stable operation and maximizing the lifespan of these intricate devices. A critical aspect of this challenge is ensuring the heat generated by each chip is efficiently dissipated, preventing unwanted thermal throttling and component failure.The fundamental challenge is the concentration of heat sources.

A single chip can produce substantial heat, and when numerous chips are densely packed, the overall heat output escalates rapidly. Maintaining proper temperatures requires sophisticated cooling systems that can efficiently extract this concentrated thermal energy. This necessitates not only robust heat sinks but also advanced cooling technologies to effectively manage the heat generated.

Thermal Challenges of Stacked Chips

The compact arrangement of stacked chips leads to several thermal challenges. Increased power density directly translates to higher heat fluxes. The small gaps between the chips can hinder natural convection and create localized hotspots. Efficient thermal pathways are vital to ensure heat dissipation, preventing overheating and potential damage to sensitive components. The need for advanced cooling mechanisms is amplified by the limitations imposed by the small form factor.

Innovative Cooling Solutions for Stacked Chips

Innovative cooling solutions are essential for effectively managing the increased thermal load in stacked chip designs. One approach is to employ advanced materials with superior thermal conductivity. These materials can facilitate more rapid heat transfer from the chips to the cooling system. Additionally, advanced cooling systems, such as micro-channels and vapor chambers, are being developed to enhance heat transfer efficiency.

Heat Dissipation Techniques

Several heat dissipation techniques are employed to manage the heat generated by stacked chips. One technique involves using thin films of high thermal conductivity materials, such as diamond or graphene, to enhance heat transfer. Furthermore, advanced heat pipes and liquid cooling systems are being explored to improve thermal management.

Materials Used for Heat Sinks

Various materials are employed for heat sinks in the context of stacked chips. Copper is a common choice due to its high thermal conductivity. Aluminum alloys are also used for their cost-effectiveness and suitable thermal properties. Advanced composites, often incorporating high thermal conductivity fillers, are increasingly utilized to achieve superior heat dissipation. Graphene and diamond are emerging materials due to their exceptional thermal conductivity, but their cost remains a factor in widespread adoption.

Thermal Management Strategies

| Strategy | Description | Advantages | Disadvantages |

|---|---|---|---|

| Heat Spreader | A layer of high thermal conductivity material placed on top of the chips. | Simple design, relatively low cost. | Limited thermal performance for high power densities. |

| Heat Pipes | Closed tubes containing a fluid that vaporizes and condenses to transfer heat. | Efficient heat transfer over a larger area. | Complexity in design, potentially higher cost. |

| Liquid Cooling | Using a liquid coolant to absorb heat from the chips. | High heat dissipation capacity, potentially higher efficiency than other methods. | Complexity in implementation, potential leakage risks. |

| Phase Change Materials (PCMs) | Materials that absorb and release heat during phase transitions. | Potential for superior thermal management, efficient heat storage. | Complexity in implementation, potentially high cost. |

Manufacturing and Fabrication

The journey from concept to a fully functional stacked chip module involves intricate manufacturing processes. These processes must be meticulously controlled to ensure the quality, performance, and reliability of the final product. Success hinges on the precise alignment of layers, the integrity of interconnects, and the ability to manage thermal stresses. The current state of fabrication techniques is pushing the boundaries of what’s possible, but challenges remain, particularly in scaling production for mass adoption.

Processes Involved in Creating Stacked Chip Modules

The creation of stacked chip modules is a multi-step process, involving several critical stages. Each stage requires sophisticated equipment and highly skilled personnel. From initial material preparation to final testing, each step is crucial in achieving a successful outcome.

- Material Preparation and Wafer Fabrication: The process begins with the selection and preparation of high-quality semiconductor materials. This includes careful control of doping concentrations and crystal structure, crucial for electrical properties. Wafers, thin slices of semiconductor material, are then fabricated using techniques like chemical vapor deposition (CVD) and sputtering to create the necessary layers. This ensures uniformity and quality in the base materials.

- Chip Fabrication: Individual chips are manufactured on the wafers, following standard integrated circuit (IC) fabrication procedures. This includes photolithography, etching, and deposition processes. The complexity of the chip design will dictate the level of detail and precision required in this phase. Different chip types, such as CPUs, GPUs, and memory chips, each necessitate specialized procedures.

- Die-to-Die Bonding: The most critical step in stacked chip fabrication is die-to-die bonding. This process involves precisely aligning and joining individual chips. Different bonding techniques are employed, such as flip-chip bonding, where the chips are bonded face-down, or through-silicon vias (TSVs). These TSVs are microscopic holes etched through the silicon die, creating pathways for interconnects between the chips.

The precision of alignment is critical for ensuring proper electrical connectivity.

- Interconnect Fabrication: Creating robust and reliable interconnects between the stacked chips is paramount. This involves using various materials and techniques to form electrical pathways. The choice of materials, such as copper or low-resistance interconnects, impacts the overall performance and reliability of the stacked chip module.

- Packaging and Testing: The final steps involve encapsulating the stacked chip module in a protective package. The package protects the delicate components from environmental factors. Rigorous testing is conducted to ensure the module meets performance specifications and reliability requirements. Testing verifies functionality, stability, and thermal behavior under various operating conditions. Failure analysis and troubleshooting are essential to ensure consistent quality.

Current State of Fabrication Techniques

Current fabrication techniques for stacked chip designs are constantly evolving. Advancements in materials science and micro-fabrication technologies are enabling higher chip densities and improved performance. However, challenges remain in scaling these techniques to meet the demands of large-scale production. Existing techniques, like TSVs, are continually refined to enhance efficiency and reduce manufacturing costs.

Potential Difficulties in Manufacturing Stacked Chips

Creating stacked chip modules presents several manufacturing challenges. One significant hurdle is the precise alignment of multiple chips during bonding. The extremely small tolerances involved in die-to-die bonding make achieving perfect alignment a significant technical challenge. Maintaining electrical integrity throughout the stacking process is another key concern. Any imperfections or misalignments can lead to performance degradation or complete failure of the stacked module.

Impact of Materials Science

Materials science plays a critical role in the successful manufacturing of stacked chips. The choice of materials for the semiconductor wafers, interconnects, and bonding agents directly impacts the electrical conductivity, thermal properties, and overall performance of the stacked chip module. The need for materials with high conductivity and low thermal resistance is paramount. Specific material properties and characteristics influence the process efficiency and overall reliability.

New materials and compositions are continuously being developed to address the unique demands of stacking chips.

Steps in the Production Process for Stacked Chips

| Step | Description |

|---|---|

| 1 | Wafer Preparation and Fabrication |

| 2 | Chip Fabrication |

| 3 | Die-to-Die Bonding |

| 4 | Interconnect Fabrication |

| 5 | Packaging and Testing |

Potential Performance Gains

The promise of stacking chips, like meticulously layering pancakes, holds immense potential for revolutionizing laptop performance. This innovative approach transcends traditional design limitations, opening doors to faster processing, improved energy efficiency, and enhanced overall user experience. By tightly integrating components and minimizing distances between them, laptops can achieve unprecedented levels of responsiveness and power.

Improved Processing Power and Speed

Chip stacking allows for a dramatic increase in the number of transistors on a given area. This translates directly into higher processing power and faster speeds. Modern CPUs, or central processing units, require intricate communication networks between different processing cores. By bringing these cores closer together through stacking, data transfer times are reduced, and the overall speed of the CPU improves.

This is analogous to having faster roads for data to travel between different parts of a city.

Enhanced Battery Life

The improved efficiency inherent in stacked chip designs can contribute significantly to extended battery life. Minimizing distances between components reduces the energy lost through heat dissipation. This thermal efficiency directly impacts the battery’s ability to power the system. Reduced heat generation, facilitated by closer proximity of components and optimized thermal management systems, allows for more power to be delivered to the device, leading to longer battery life.

Consider the advancements in mobile phones; recent models often boast longer battery life due to optimized power management.

Performance Improvements in Related Technologies

The concept of chip stacking isn’t entirely new. We’ve seen similar advancements in other technologies, like mobile phones and high-end gaming PCs. These devices leverage tightly integrated systems and efficient cooling solutions to achieve impressive performance gains. For example, the latest generation of smartphones, with their compact yet powerful processors, often demonstrate remarkable processing speed and long battery life, showcasing the potential of integrated design.

Comparison of Stacked vs. Non-Stacked Chips

| Feature | Non-Stacked Chip | Stacked Chip |

|---|---|---|

| Processing Speed | Moderate | High |

| Power Consumption | Higher | Lower |

| Heat Generation | Significant | Minimal |

| Performance Per Unit Area | Lower | Higher |

| Battery Life | Average | Extended |

This table illustrates the potential advantages of stacking chips. The significant difference in processing speed, reduced power consumption, and minimized heat generation highlight the potential benefits for laptop users. Note that specific performance numbers will vary based on the specific design and implementation.

Power Consumption and Efficiency

Pancake-style chip stacking, while promising massive performance boosts, necessitates careful consideration of power consumption. The intricate proximity of components in a tightly stacked architecture can lead to higher heat dissipation, and thus, increased energy demands. Optimizing power efficiency is crucial for practical adoption of this technology. Balancing performance gains with energy use is paramount to widespread acceptance of these advanced chips.Stacked chips, though potentially faster, are not inherently more energy-efficient.

The smaller footprint and denser interconnects can present unique challenges in heat management, potentially increasing overall power consumption. Strategies for power optimization in these configurations are critical for their success. Clever design choices and meticulous implementation of power management techniques are essential to mitigate these concerns and enable efficient operation.

Impact of Stacking on Power Consumption

The proximity of components in stacked architectures can lead to increased heat generation due to higher current density and more frequent switching activity. This can necessitate larger cooling solutions, leading to higher power consumption compared to traditional designs. The smaller interconnects, while aiding in faster data transfer, also introduce higher resistance, potentially leading to greater power dissipation. In essence, the density gains need to be carefully balanced against potential power losses.

Optimizing Power Efficiency in Stacked Chips

Several strategies can mitigate the power consumption increase associated with stacking. One critical approach involves employing advanced materials and techniques for improved thermal conductivity. These materials allow heat to dissipate more efficiently, reducing the need for large, energy-intensive cooling systems. Furthermore, sophisticated power management units (PMUs) play a crucial role in dynamically adjusting power delivery based on real-time performance needs.

Such units can significantly reduce idle power consumption.

Power-Efficient Designs in Related Technologies

Power-efficient design principles are not new. Techniques like dynamic voltage and frequency scaling (DVFS) are already successfully implemented in modern CPUs. DVFS adjusts the operating voltage and frequency of the processor based on the workload, leading to significant energy savings during periods of low activity. Similar strategies can be employed in stacked chip designs to optimize power consumption.

For example, in mobile devices, the use of low-power processors and advanced battery management systems is already standard practice. This exemplifies the importance of energy efficiency in modern technology.

Power Management Techniques in Stacked Chips

Power management in stacked chips involves a combination of hardware and software solutions. Hardware components include sophisticated thermal sensors and controllers that monitor temperature and adjust power delivery accordingly. Sophisticated software algorithms can optimize the allocation of processing power based on the specific task and thermal constraints. Moreover, careful design choices in the placement of power delivery networks (PDNs) and interconnects minimize resistance and associated power loss.

Table of Power Consumption Metrics

| Chip Configuration | Power Consumption (Watts) | Performance (GFlops) |

|---|---|---|

| Traditional 2D Chip | 10 | 5 |

| 4-Layer Stacked Chip (Optimized) | 12 | 10 |

| 4-Layer Stacked Chip (Baseline) | 15 | 10 |

Note: The values in the table are illustrative and depend heavily on the specific design and optimization strategies employed. Furthermore, performance is measured in GFlops (Giga Floating-Point Operations per Second) for a relative comparison to processing power.

Imagine stacking computer chips like pancakes – it could revolutionize laptops! This innovative approach might drastically improve processing power, leading to faster performance and more efficient use of energy. Knowing how to download videos from YouTube for offline viewing on your Android device is also important, especially if you’re on the go. Check out this helpful guide on how download videos youtube offline android for some practical tips.

Ultimately, this new chip stacking method promises a significant advancement in laptop technology, making them more powerful and portable than ever before.

System Integration

Pancake-style chip stacking, while promising significant performance boosts, introduces complex system integration challenges. Successfully integrating these vertically-stacked chips into a laptop motherboard demands careful planning and execution, encompassing everything from electrical connections to software drivers. The reward, however, could be a leap forward in laptop performance and portability.

Integration into the Laptop Motherboard

The integration of stacked chips necessitates a reimagining of the laptop motherboard’s architecture. Traditional motherboard designs, optimized for planar components, need substantial redesign to accommodate the vertical stacking. This includes the placement of power delivery networks, cooling solutions, and signal routing pathways. The precise arrangement of these components will directly impact the overall performance and reliability of the system.

A crucial aspect is the need for efficient thermal management, given the increased heat density resulting from the close proximity of components. Specialized thermal interfaces and cooling systems will be essential to maintain optimal operating temperatures.

Challenges in Connecting Components

Connecting various components on a stacked chip system presents significant hurdles. The high density and intricate interconnections require precise manufacturing processes and robust electrical pathways. Maintaining signal integrity across the stacked layers is critical for preventing data loss or corruption. Minimizing signal delay and crosstalk between layers will be vital. The complexity of routing signals and ensuring low impedance paths throughout the various layers of the stack is a significant challenge that needs innovative solutions.

Software and Firmware Implications

Software and firmware drivers will require substantial updates to manage the new hardware architecture. Drivers must efficiently handle communication between the stacked chips and the rest of the system. The operating system must also be modified to handle the unique characteristics of the stacked chip design. A potential challenge is that drivers might not always be able to optimize all the functionalities to their maximum potential.

Potential for Future System Architecture Changes

The integration of stacked chips could lead to a significant shift in laptop system architecture. The reduced footprint and improved performance may enable new form factors and design possibilities. For example, thinner and lighter laptops with more powerful processing capabilities could become a reality. We might also see a move towards more specialized hardware for specific tasks, integrated into the stack.

Block Diagram of a Laptop System using Stacked Chips

(A simple block diagram, depicting the key components of a laptop system using stacked chips, would be displayed here if an image was allowed. The diagram would show the processor (CPU), memory (RAM), graphics processing unit (GPU), and other essential components integrated vertically in a stack. Connections between the stack and other components, such as input/output (I/O) devices and the system bus, would be clearly labeled. This would illustrate the integration of the stack into the overall system architecture. The diagram would also depict the thermal management solutions, including heat sinks and cooling fans, integrated into the design.)

Impact on Laptop Design

Pancake-style chip stacking promises a revolution in laptop design, offering the potential for significant advancements in size, weight, and performance. This innovative approach, by consolidating multiple components onto a smaller footprint, could reshape the very definition of portability and power. The implications extend beyond simply making laptops smaller; it fundamentally alters the design possibilities and opens avenues for previously unimaginable features.

Laptop Thinness and Weight Reduction

The reduced size and improved efficiency of stacked chips allow for a significant reduction in the overall thickness and weight of laptops. This translates to enhanced portability and a more comfortable user experience. Current laptops, even ultra-thin models, often struggle to balance performance with portability. The new design approach allows manufacturers to pack more powerful components into a smaller volume, pushing the boundaries of what is possible in portable computing.

Form Factor Evolution, Why stacking chips like pancakes could mean a huge leap for laptops

The traditional laptop form factor, while effective, is now being challenged by the possibilities of chip stacking. The ability to consolidate components into a smaller volume paves the way for more innovative form factors, beyond the standard clamshell. Imagine laptops that can fold or unfold, seamlessly transitioning from a compact tablet to a full-sized workstation. This is not a futuristic concept; companies are already exploring flexible displays and foldable devices, and chip stacking accelerates the trend toward modularity and customization.

Compatibility with Different Form Factors

| Form Factor | Compatibility with Stacked Chips | Potential Advantages |

|---|---|---|

| Clamshell | High | Existing design principles can be easily adapted for stacked chip integration. |

| Convertible | Medium | The flexibility of the hinge allows for adjustments in thickness and size to accommodate stacked components. |

| 2-in-1 | High | The modular nature of 2-in-1 devices makes them well-suited to incorporate the compact design benefits of stacked chips. |

| Foldable | High | Foldable devices can benefit greatly from the space-saving nature of stacked chips, potentially enabling more powerful configurations in a compact form factor. |

| Tablet | Medium | Integration will depend on the specific design, but the potential for a more powerful tablet is significant. |

This table illustrates the varying degrees of compatibility between different laptop form factors and stacked chip technology. The clamshell and 2-in-1 designs are well-positioned to leverage the benefits, while foldable and tablet designs show promise for innovation in this area. Each design presents unique opportunities and challenges for implementation.

Example: The “Ultra-Slim” Laptop

Imagine a laptop thinner than a tablet, yet packing the power of a desktop. This is not a far-fetched vision. The miniaturization enabled by chip stacking allows for the creation of such a device, potentially exceeding current conceptions of portable computing. The impact on weight and design would be substantial, offering a revolutionary shift in portability.

Summary: Why Stacking Chips Like Pancakes Could Mean A Huge Leap For Laptops

In conclusion, stacking chips like pancakes presents a compelling path towards a new generation of laptops. While significant challenges remain in thermal management, manufacturing, and system integration, the potential rewards are enormous. Imagine laptops that are not only incredibly powerful but also incredibly compact and efficient. This innovative approach could revolutionize the portable computing experience, pushing the boundaries of what’s possible in terms of performance and design.

The future of laptops may very well be stacked.